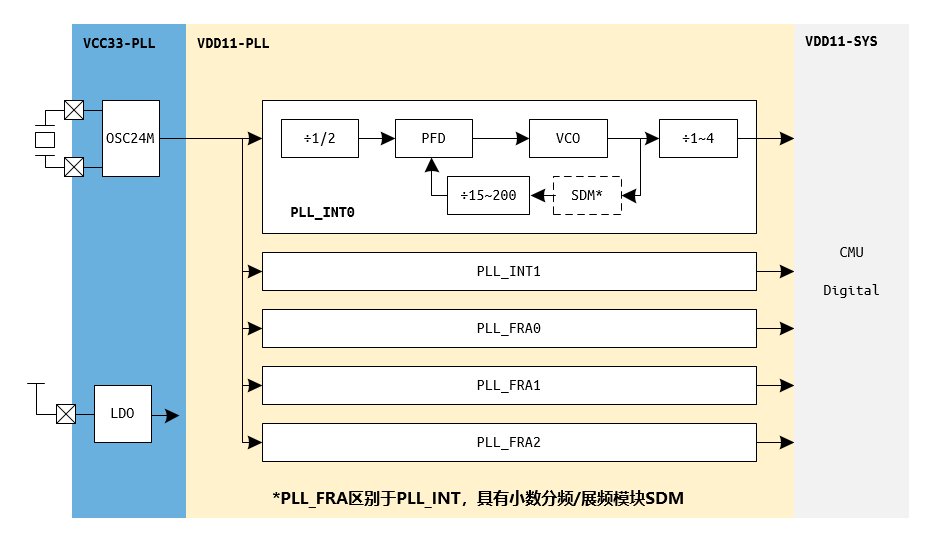

PLL

模拟电路 PLL 用于产生时钟供给整个芯片。

CMU PLL 用途及特性列出了各个 PLL 的用途及特性。

| 名称 | 用途 | 典型频率 | 展频或小数分频 |

|---|---|---|---|

| PLL_INT0 | CPU | - | 不支持 |

| PLL_INT1 | AXI/AHB/APB/CE/DE/GE/VE/DVP/PWMCS/UART | 1.2GHz | 不支持 |

| PLL_FRA0 | DRAM/SDMC/SPI | 1008MHz | 展频 |

| PLL_FRA1 | I2S/AUDIO | 491.52MHz451.584MHz | 小数分频 |

| PLL_FRA2 | LCD/LVDS/MIPI_DSI | 展频 |

PLL 内部结构如下图所示, PLL 频率计算公式为:PLL_OUT = 24MHz÷(P+1)×(N+1+(F÷(2^17-1)))÷(M+1)。