时钟和电源

POWER

对于电源系统,可选择以下任一方案:

| 方案 | 描述 | 优点 | 缺点 |

|---|---|---|---|

| 1 | 芯片 VCC33_IO(3.3 V/ 200 mA)、 VDD11_SYS(1.1 V/ 200 mA) 和 LDO18(1.8 V/ 200 mA)全都使用外部 DCDC 供电。 | 发热最小、功耗最小 | 成本最高 |

| 2 | 芯片 VCC33_IO(3.3 V/ 200 mA)和 VDD11_SYS(1.1 V/ 200 mA) 采用外部 DCDC 供电,LDO18 使用内置 LDO 供电。 | DCDC 电源效率高功耗降低 | 器件多、成本变高 |

| 3 | 芯片 VCC33_IO(3.3 V/ 300 mA)采用单 3.3 V 供电,VDD11_SYS 和 LDO18 使用内置 LDO 供电。 | 电路简洁、节省成本 | LDO 电源效率低功耗变高 |

- 方案 1:芯片 VCC33_IO(3.3 V/ 200 mA)、 VDD11_SYS(1.1 V/ 200 mA) 和 LDO18(1.8 V/ 200 mA)全都使用外部 DCDC 供电。优点是发热最小、功耗最小;缺点是成本最高。

- 方案 2:芯片 VCC33_IO(3.3 V/ 200 mA)和 VDD11_SYS(1.1 V/ 200 mA) 采用外部 DCDC 供电,LDO18 使用内置 LDO 供电。优点是 DCDC 电源效率高功耗降低;缺点是器件多、成本变高。

- 方案 3:芯片 VCC33_IO(3.3 V/ 300 mA)采用单 3.3 V 供电,VDD11_SYS 和 LDO18 使用内置 LDO 供电。优点是电路简洁、节省成本;缺点是 LDO 电源效率低功耗变高。

-

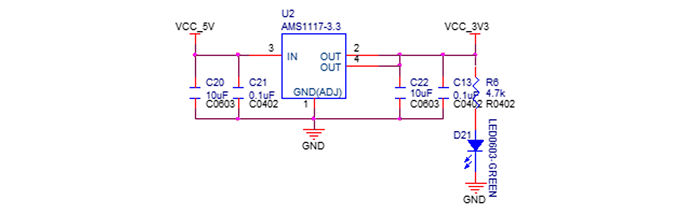

图 1. 芯片 VCC33_IO 单 3.3 V 电源供电原理图 -

内置 LDO18,芯片复位时默认关闭,SDK 可配置输出 1.8 V 供 PSRAM 使用,LDO18 引脚外部接 10 uF + 0.1 uF 旁路电容即可。

-

内置 LDO1x,芯片复位时默认开启,SDK 可配置输出 1.1 V 供 VDD11_SYS 使用,VDD11_SYS 引脚外挂 10 uF + 0.1 uF 旁路电容即可。

-

内置 LDO25,默认开启,供内部模拟模块使用,LDO25 引脚外部接 1 uf 旁路电容即可。

-

- 上下电时序要求

- 无上下电时序要求。

- 内置 24M OSC,无需外挂晶振。

- 复位信号内置约 30 KΩ上拉电阻和去抖滤波,不使用可直接悬空,若外挂电容建议不超过 4.7 uF。上电完成后,复位自动释放。

SYSTEM

| 信号名 | 信号说明 | 应用说明 |

|---|---|---|

| UBOOT | 升级模式配置 | 如需进入升级模式,可在 UBOOT 或 bootloader 配置任意 IO 为下拉检测或上拉检测,SDK 默认使用 PA0 下降沿检测,建议预留按键或跳线。 |

| RESET | 芯片复位脚 | 内部 RC 上拉,低电平复位,可悬空,建议预留按键或跳线。 |

PLL

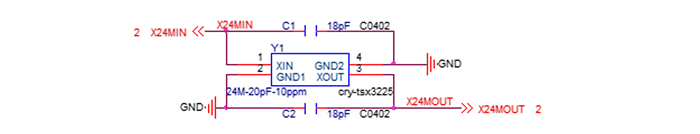

PLL 需外接 24MHz 晶振:

- 外部 24 MHz 晶振精度要求小于 ± 20 ppm,匹配电容根据晶体负载电容选择。

- PLL_XO 建议串联 0R 电阻,便于调试振荡幅度。

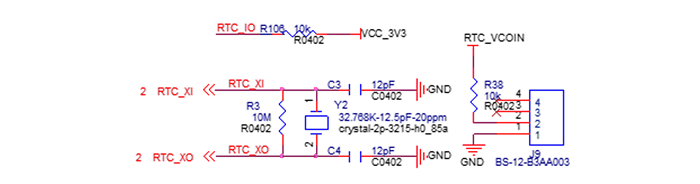

RTC

内置 RTC,功耗约 2.8uA,使用 RTC 功能需外接 32.768KHz 晶振

- 外部 32.768KHz 晶振精度建议小于 ±10ppm,匹配电容根据晶体负载电容选择。

- RTC_XI 和 XO 之间并接10M以上电阻,可用于频率微调。

- RTC_IO 为 OD 输出,使用时需要外挂上拉电阻,上拉电平不超过 5V,可用于 RTC 唤醒或输出 32K 时钟。

- 若不考虑掉电保持,RTC_VCOIN 可悬空,内部有二极管通路从 VCC33_IO 取电。