版本

由于 FPGA 资源有限,无法实现芯片的全部逻辑,也由于模块的验证需求不尽相同,开发一款芯片往往会实现多个 FPGA

版本,通过制作 bitfile 选择项不同,实现不同资源的 bitfile,FPGA 版本制作 bitfile选择项目如下表所示。

-

PROCESS/ MEMORY/ DISPLAY/ ENGINE 选择模块为互斥,只能从三/二选一

-

除了部分接口不出IO,其他模块默认包含在FPGA中

| 分类 | 选择1 | 选择2 | 选择3 | 备注 |

|---|---|---|---|---|

| PROCESS | CPU | PCIE | - | - |

| MEMORY | DDR2 | DDR3 | NDDR | - |

| DISPLAY | LVDS | MIPI | NLCD | 选择1包含LVDS&RGB |

| ENGINE | CE | GA | VE | 选择1包含CE&SID |

处理器选择说明

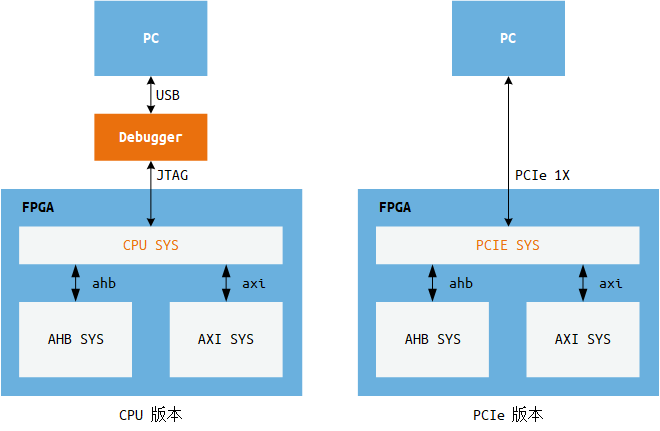

PROCESS选择项为CPU/PCIE,两者差别如下图所示, 左边是选择CPU,右边是选择PCIE。

CPU 选择项版本用于各种功能验证以及操作系统调试; CPU选择项版本等同于ASIC实现,通过PC机连接仿真器,仿真器连接到FPGA的JTAG接口,控制CPU实现访问。

PCIE选择项版本主要用于DE/GE/VE等具有大吞吐数据的模块自动化验证; PCIE选择项版本通过PC的PCIe连接到FPGA PCIe,FPGA实现PCIe转AXI,使用AXI进行传输和控制; 具有数据吞吐量大(2.5Gbps,当前使用<5MB,后续需要进一步提升)且方便自动验证。

接口模块说明

由于 FPGA IO 限制,接口模块往往没有包括 ASIC 所有模块;主要表现为在有多套一样的模块时, FPGA套数没有实际芯片那么多,具体套数如下表所示。 接口IO分配的具体位置可参考附录1。

| 模块 | 套数 | 备注 |

|---|---|---|

| UART | 3 | UART0: 2线用于DEBUG,UART1/2: 3线用于RS485验证 |

| TWI | 4 | TWI0/1:CON,TWI2: AUDIO-AC101,TWI3: DVP/MIPI-CSI |

| CIR | 2 | - |

| CAN | 2 | MIPI |

| GMAC | 2 | GMAC0: RMII 100M,GMAC1: RGMII 1000M |

| USB | 2 | USB0: DEVICE,USB1: HOST |

| I2S | 1 | 接AC101 |

| DMIC | 1 | - |

| SPK_OUT | 1 | - |

| SPI | 3 | SPI0/1用于SPI NAND/NOR,SPI2用于PWMCS ADC使用 |

| SDMC | 3 | - |

| PWM | - | - |

| ADCIM | - | - |