xSPI 支持的协议模式

xSPI 模块约定了以下缩写描述:

- S:SDR 模式

- D:DDR 模式

- 数字1/2/4/8:输出 IO 的数量,即分别输出一个/两个/四个/八个 IO。

举例说明如下:

- 8D-8D-8D:CMD-ADD-DATA 都以八个 IO 输入输出且为 DDR 模式

- 1S-1S-8D:CMD-ADD 都以一个 IO 输出且为 SDR 模式,DATA 则八个 IO 输入输出且为 DDR 模式。

为了灵活配置各协议,在 CMD-ADD-DATA 单个完整传输中,各部分结构都可为 SDR/ DDR 以及 IO 独立配置, 此独立配置以查找表的方式存储,详细见。本节仅仅列出典型协议行为。

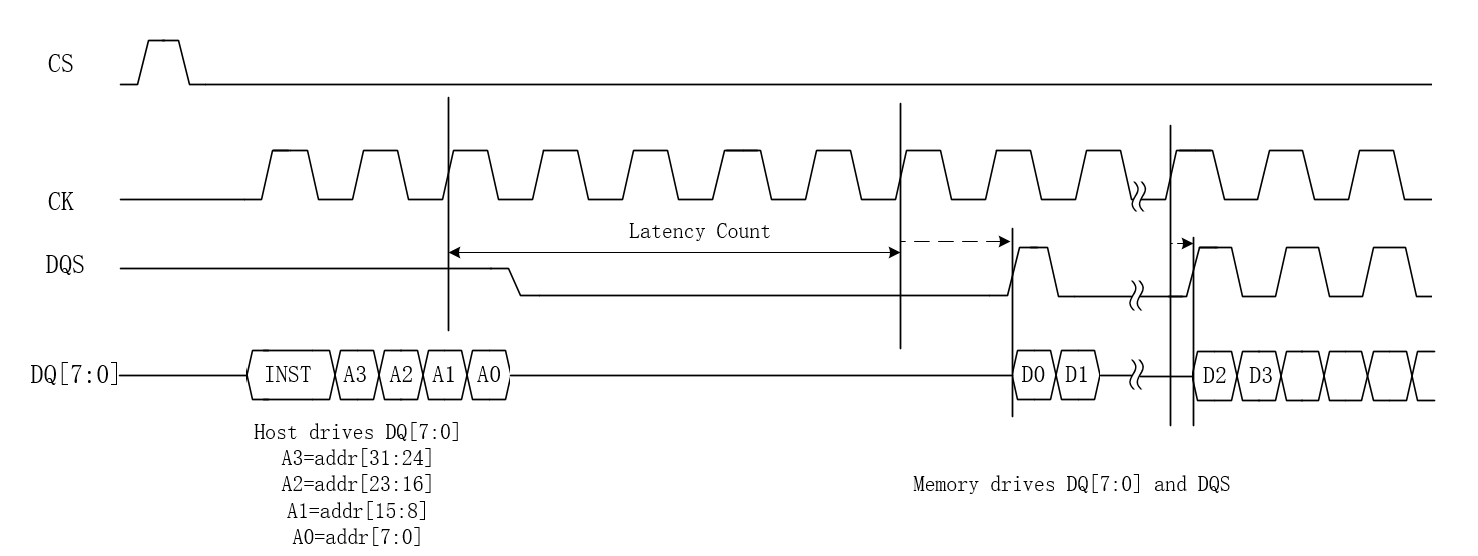

Xccela 协议

中以 8D-8D-8D 为例进行说明,Xccela

协议的工作模式如下所示。

- Host 发起 CMD-ADD。注: 下列 CMD 占两个采样沿,ADD 占一个采样沿,之后接着可配的 Dummy cycles;

图 1. Xccela读操作 - dummy 期间 Memory device 获得 DQS 线权,在约定的 dummy cycles 后,接着的 CK 触发 Memory device

读数据输出;此时 host 以 DQS 采样时钟。注: CK 与 DQS 存在一定的延时,DQS 与 DATA 边沿对齐。

- 在 memory device 进行跨行边界读取数据时,DQS 会在行尾数据保持状态,如 所示。

图 2. Xccela跨行边界读操作

中以 8D-8D-8D 为例。CMD-ADD 以及 Dummy

cycles 与读操作一致,DQS 由 host 占据线权,作为 data mask。

注: CK 与 DATA

中心对齐,DQS 与 DATA 边沿对齐。其中D0、D3 以及 D4 被屏蔽,不作为有效数据写进 memory device。

Hyperbus 协议

中以 8D-8D-8D 为例进行说明。

- Hyperbus 中 CA 存在两个 byte 的 CMD,第二个 byte CMD 定义为 CMD-Ex (Command-Extension),用于填充高位地址,具体实现见 。

- 在 Host 发起CA期间,Host 检测 RWDS 的电平状态;

- 若 RWDS 电平为低,则等待配置好的 dummy cycles;

- 若 RWDS 电平为高,则等待2倍的已配置dummy cycle 数,接着的CK触发Memory device读数据输出,此时host以DQS采样时钟。

注: CK与DQS存在一定的延时,DQS 与 DATA 边沿对齐,也会存在跨行边界读取数据RWDS等待过程。

Hyperbus写操作图中以 8D-8D-8D

为例进行说明。

- CA 与读操作一致,在 Dummy cycles 期间占据 RWDS 线权。注: 写操作中CK与DATA中心对齐,RWDS与DATA边沿对齐。

- 其中 RWDS 也作为 data mask,图示 Dn A,Dn+2 B以及Dn+3 A被屏蔽,不作为有效数据写进memory device。

- Host发起 CA(Command-Address),其中 CA 各 bit 的定义如所示。

| CA bit | Defined | Function |

|---|---|---|

| 47 | R/W | 指示该命令为读或者写操作

|

| 46 | Address space | 指示该命令为内存或者寄存器访问

|

| 45 | Burst type | 指示该命令的突发类型

|

| 44-16 | Row and upper column address | 32位地址系统中的A31-A3 |

| 15-3 | reserved | 预留未来行地址扩展,补0 |

| 2-0 | Lower column address | 32位地址系统中的A2-A0 |

OPI 协议

图中以 8D-8D-8D 为例进行说明。

- Host 发起 CMD-ADD,之后接着可配的 Dummy cycles,dummy 期间 Memory device 获得DQS线权。

- 在约定的 dummy cycles 后,接着的 CK 触发 Memory device 读数据输出,此时host以DQS采样时钟。注: CK 与 DQS 存在一定的延时,DQS 与 DATA 边沿对齐。

另外,在memory device进行跨行边界读取数据时,也会存在跨行边界读取数据DQS等待过程。

图中以 8D-8D-8D 为例进行说明。

- CMD-ADD 以及 Dummy cycles 与读操作一致,DQS 由 host 占据线权,作为采样时钟;DM 作为 data mask。注: DQS与DATA中心对齐,DM与DATA边沿对齐。

- 写操作中,D3 以及 D5 被屏蔽,不作为有效数据写进 memory device。

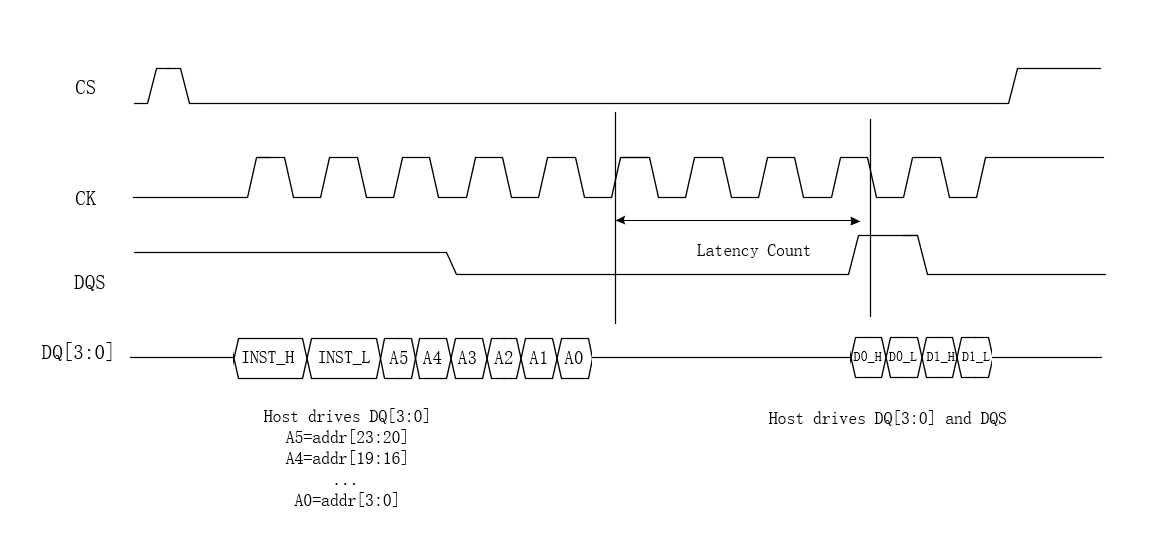

QPI 协议

图中以 8D-8D-8D 为例进行说明。

- Host 发起 CMD-ADD,之后接着可配的 Dummy cycles,dummy 期间 Memory device 获得 DQS 线权。

- 在约定的 dummy cycles 后,接着的 CK 触发 Memory device 读数据输出,此时 host 以 DQS 采样时钟。注: CK与DQS存在一定的延时,DQS与DATA边沿对齐。

- 另外,在 memory device 进行跨行边界读取数据时,也会存在跨行边界读取数据 DQS 等待过程。

图中以 8D-8D-8D 为例进行说明。

- CMD-ADD 以及 Dummy cycles 与读操作一致,DQS 由host占据线权,作为采样时钟;DM作为data mask。注: DQS与DATA中心对齐,DM与DATA边沿对齐

- 写操作中,D0 被屏蔽,不作为有效数据写进 memory device。

Octal SPI协议

图中以 1S-1S-8S 为例进行说明。

- DQ[0] 输出 CMD-ADDR,等待约定的 dummy cycles 后,DQ[7:0] 进行数据输入输出传输。

- 也会存在1S-8S-8S,1D-1D-8D 等格式,此部分不列举图示。

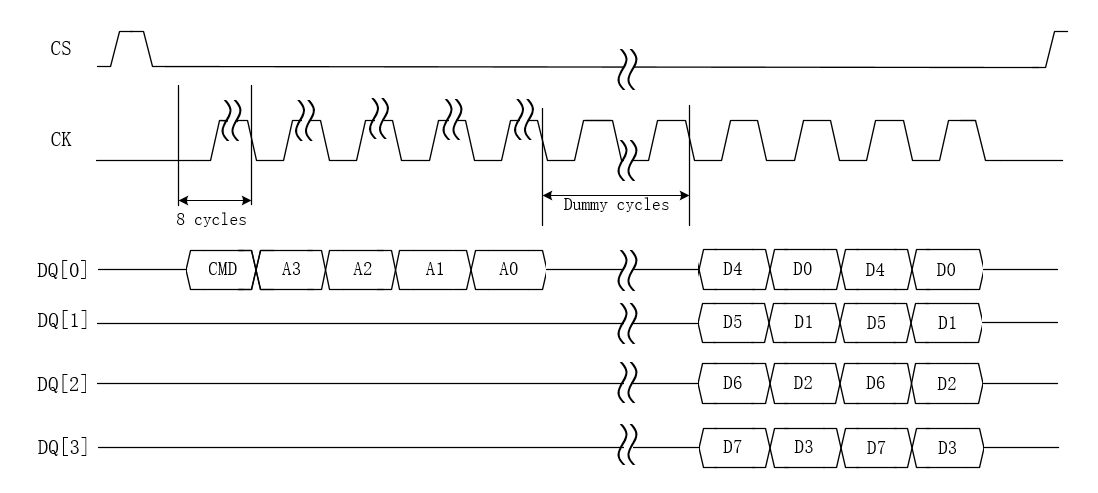

Ouad SPI协议

图中以 1S-1S-4S 为例进行说明。

DQ[0]输出CMD-ADDR,等待约定的dummy cycles后,DQ[3:0]进行数据输入输出传输。也会存在1S-4S-4S,1D-1D-4D等格式,此部分不列举图示。

双线 SPI 协议

图中以 1S-1S-2S 为例进行说明。

DQ[0]输出CMD-ADDR,等待约定的dummy cycles后,DQ[1:0]进行数据输入输出传输。也会存在1S-2S-2S,1D-2D-2D 等格式,此部分不列举图示。

单线 SPI 协议

图中以 1S-1S-2S 为例进行说明。

DQ[0] 输出 CMD-ADDR,等待约定的 dummy cycles 后,DQ[1] 进行数据输入传输。