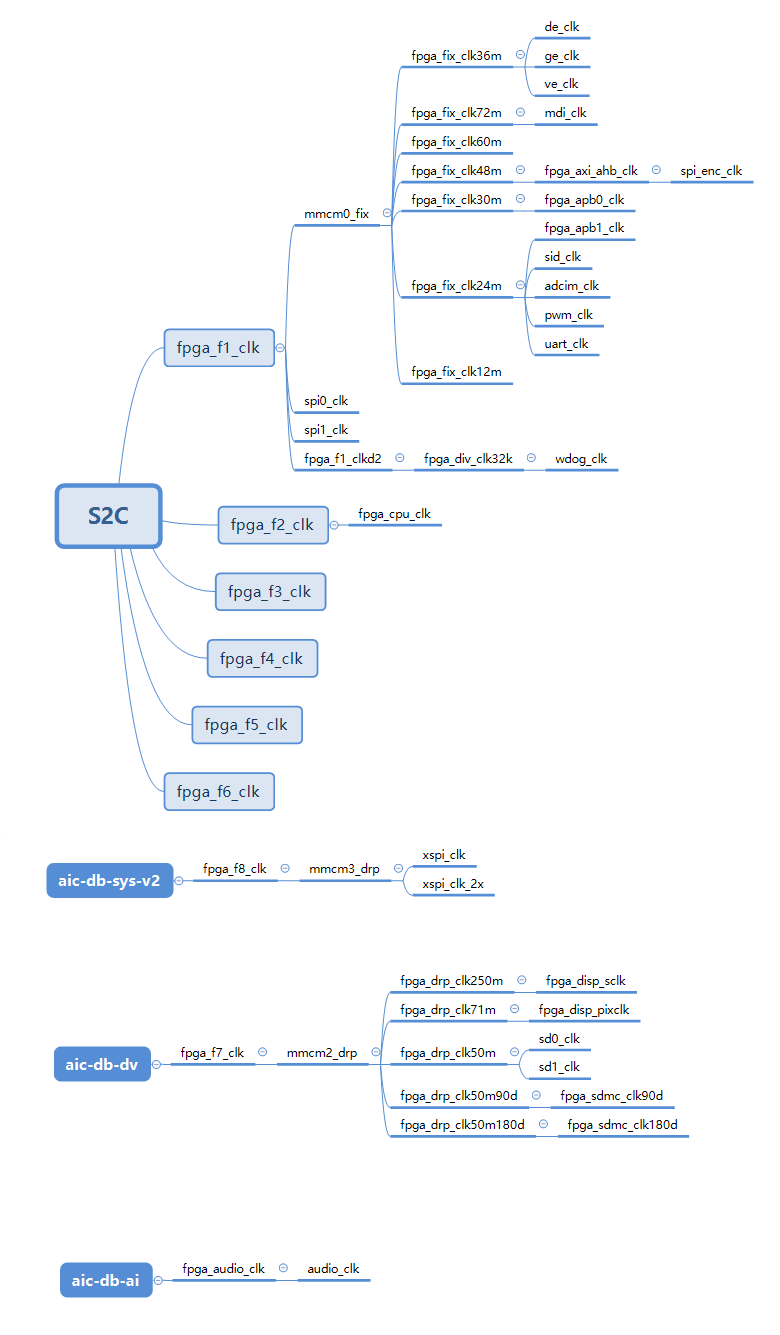

时钟

FPGA 时钟管理原则如下:

-

CMU 中模块的复位有效,但时钟 Gating 无效,不关闭。

-

CMU 无 MUX 选择,每个模块固定时钟输入。

注: CMU 的 RST 控制位仍有效。

#concept_ljw_vj3_pzb__fig_qyv_mlz_4zb图示中:

-

CPU/ AXI 可分别配置频率,通过烧写 bitfile 时配置 FPGA 输入时钟频率实现。

-

GMAC/ LCD/ SDMC 可动态调整频率,通过配置 DRP 寄存器修改 FPGA 内部 PLL 实现。

-

CLOCK3/ CLOCK5/ CLOCK6/ MMCM BANK70 用于扩展使用。